Jk フリップフロッ プ 第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt DownloadTフ リップフロップの入力の性質を決定する準備と して,そ の出力が計数フレームの最終位置で示す特徴 と,そ の位置から時間的にさかのぼったとき,そ の位 数に関連したビット数だけ連続して最終位置で示す0 または1の 値と同じ値をとり,特 にこれが1の とき図4-4(a)の回路はSRラッチ(Set-Reset latch)と 呼ばれます.SRフリップフロップと呼ばれることも ありますが,本稿ではSRラッチとしてフリップフロ ップと区別します.以降のSRラッチに制御端子を付 け足したものをフリップフロップとし 右のRSフリップフロップ回路のシミュレーションを例として、シミュレータの操作方法を述べます。

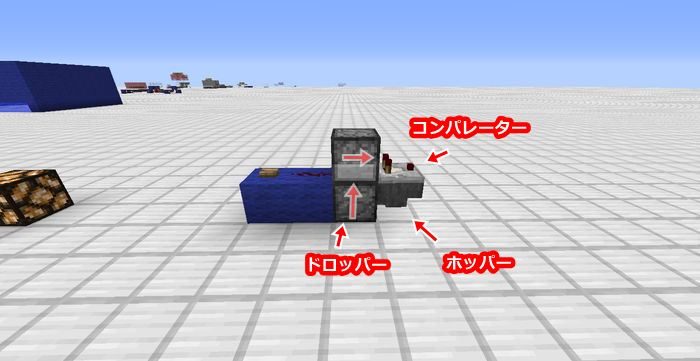

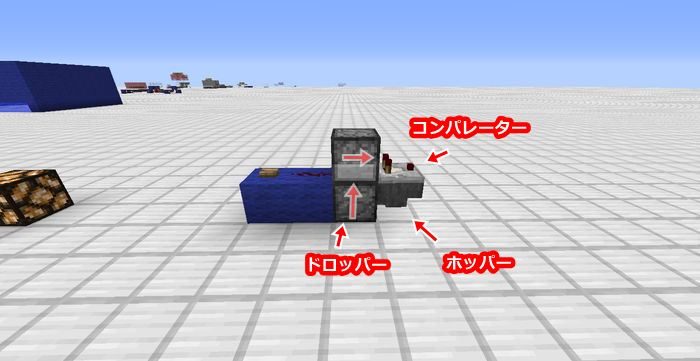

マイクラ ボタンでon Off切り替える小型のtフリップフロップ回路を色々探してみた 役に立つと思っている

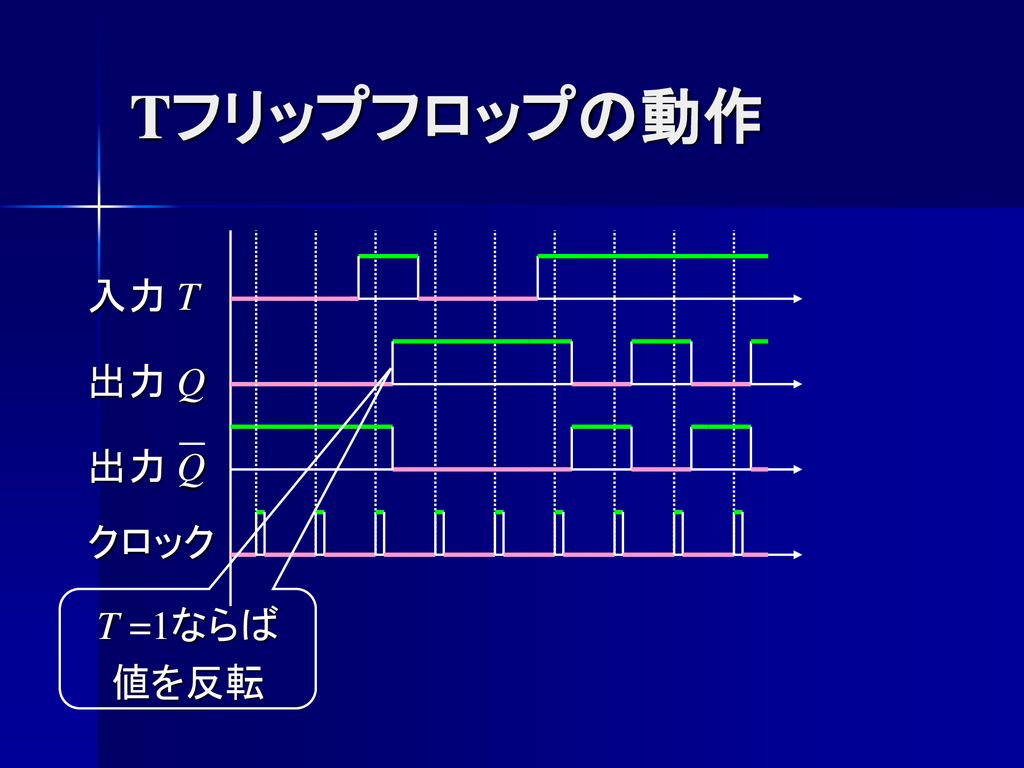

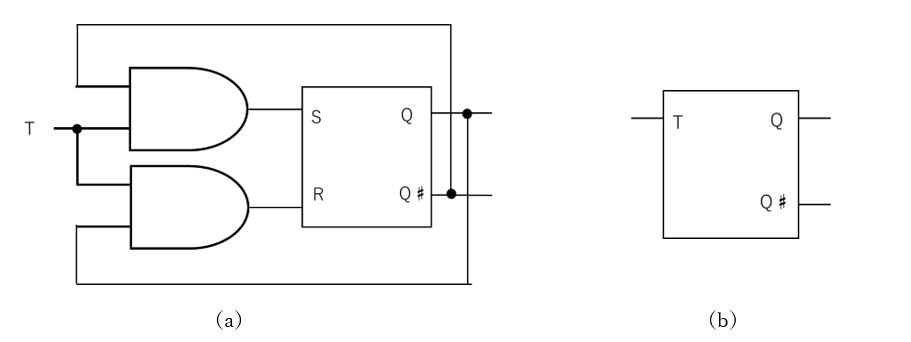

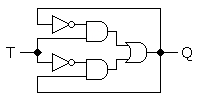

Tフリップフロップ回路

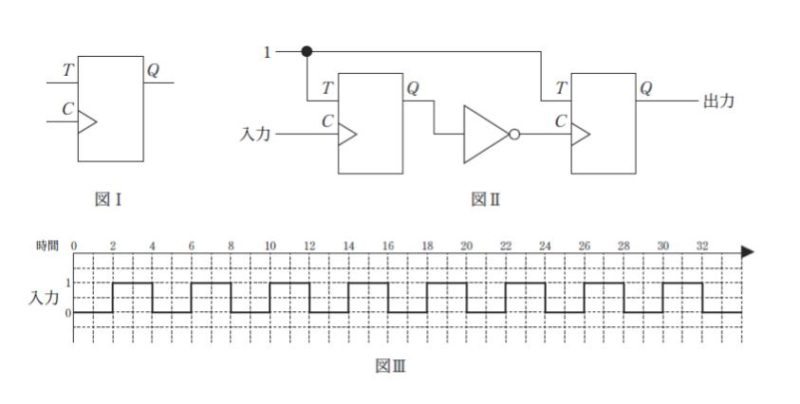

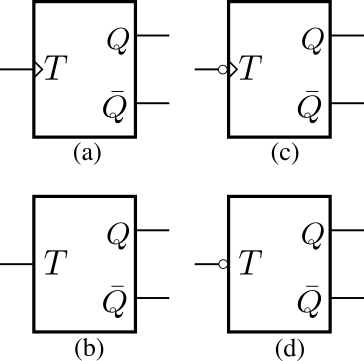

Tフリップフロップ回路-小さくすればよいのですが、 もっと確実な方法としては、フリップフロップを2段設けて、 クロックの立ち上がりで第1のフリップフロッ プ(マスター・セル) をセットし、クロックの立ち下がりで第2のフリップフロップ (スレーブ・セル)に信号を渡すようにします。フリップフロップはその構造と機能によってRS型(SR型とも呼ばれる。 SetResetの略)、JK型(語源不明)、D型(Delayedの略)、T型(Toggleの略)といった種類に分類される。 回路の種類 ラッチ回路 る.この手法には順序回路に対して故障検出率の高いテス ト・パターンを生成するとこが難しいという問題がある. この問題を解決するため,回路内のFF(フリップフロ

フリップフロップ

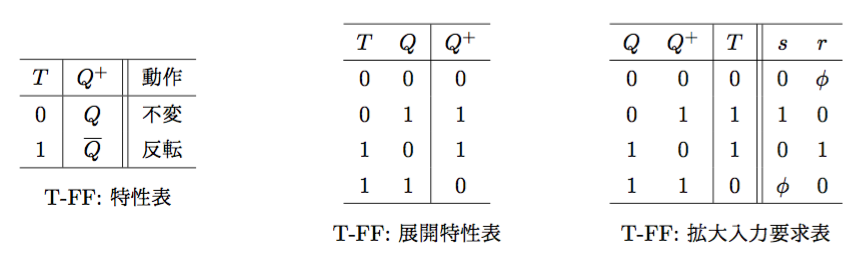

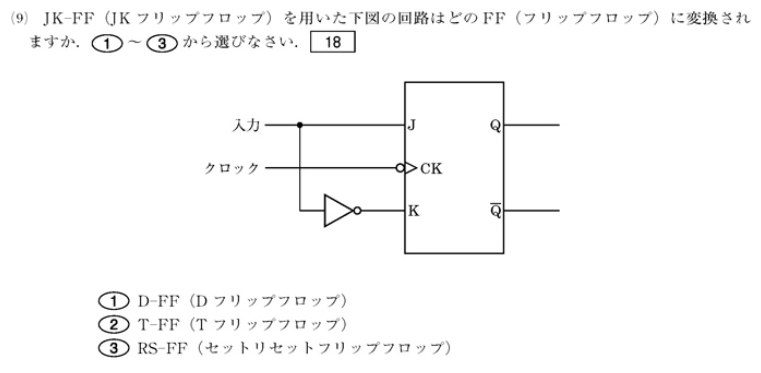

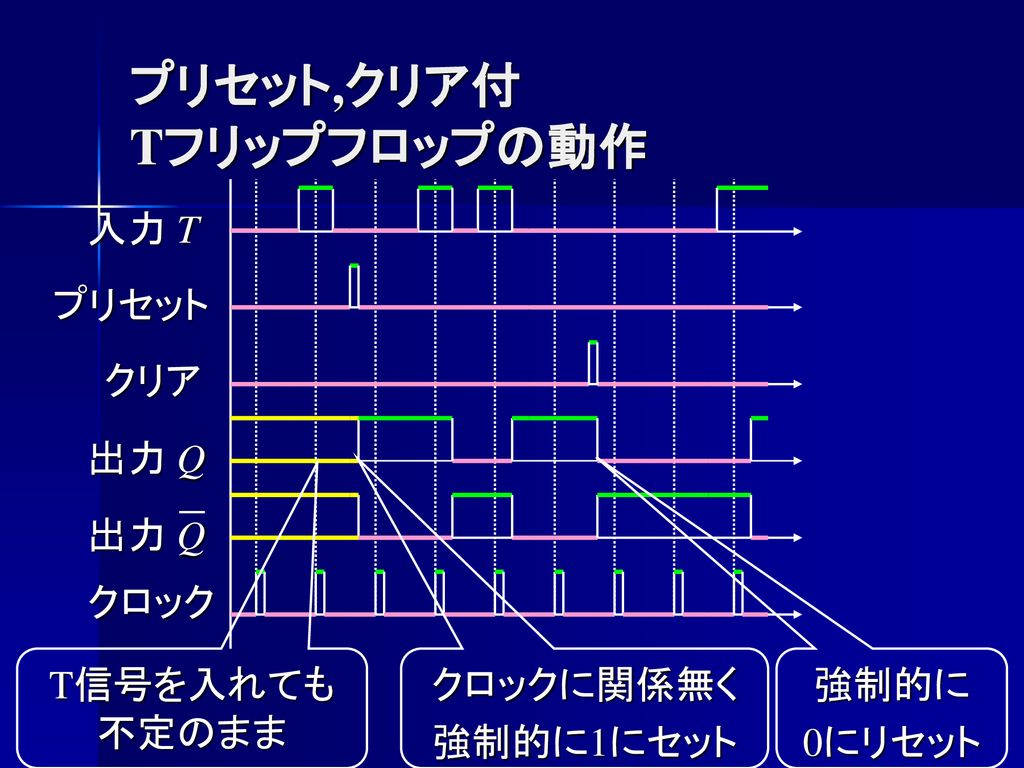

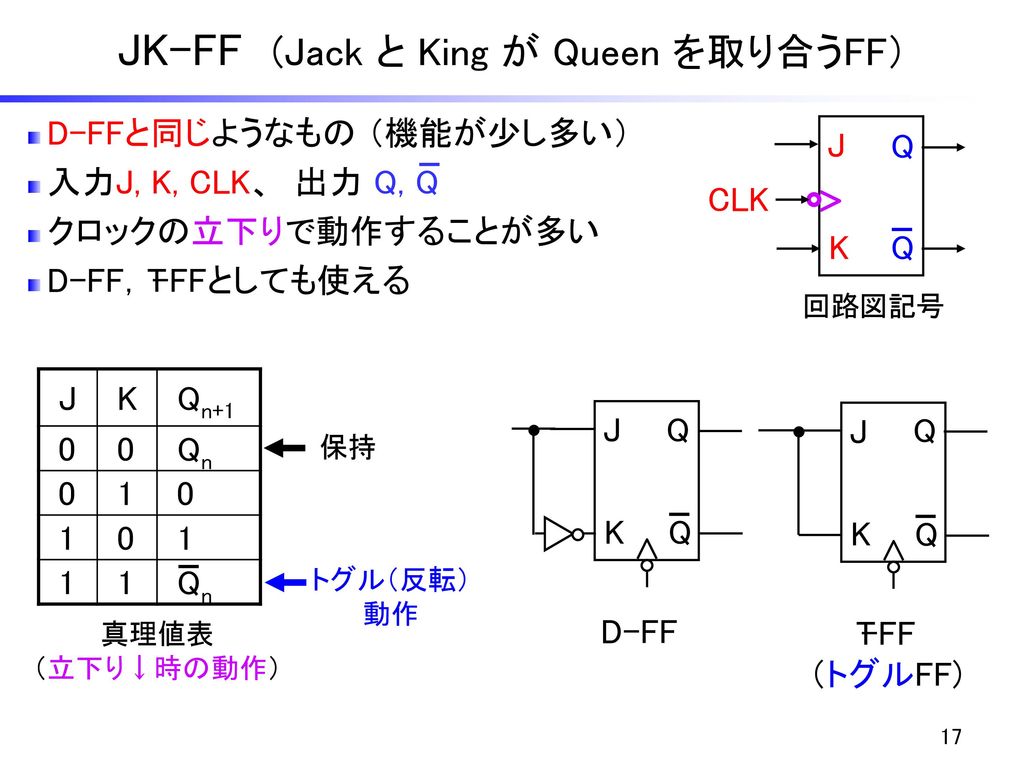

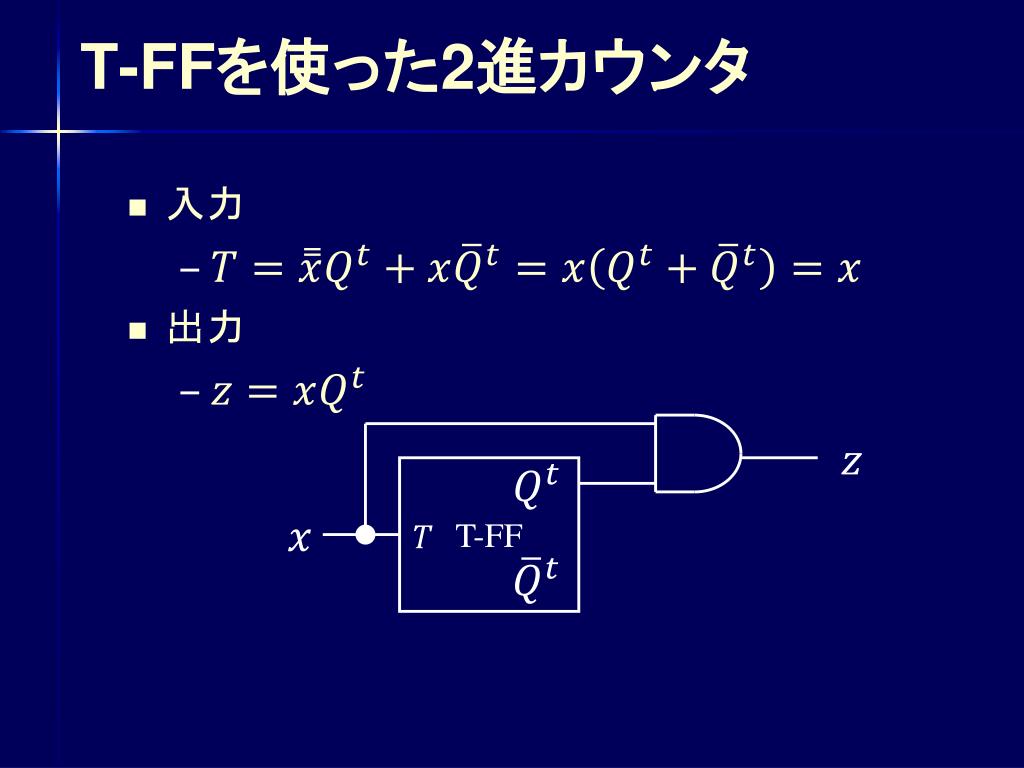

Rsフリップフロップ回路とjkフリップフロッ プ回路について予習してください。科: 必須・選択 開講時期 単位 時間/週 内線電話番号 no ① ② ③ ④ ⑤ ⑥ ⑦ ⑧ ⑨ ⑩ 試験 小テスト レポート 制作物 成果発表 その他 合計 60 30 10 100 10今回はその初めとして一番シンプルなフリップフロップについて t型フリップフロ ップ510,5,530のロック解除確認後、1ビ ットカウンタ4へ有効エッジが印加される。 その有効エ ッジの印加タイミングを調整するのが、タイミング制御 回路14である。Tフリップフロップの動作表 jkフリップフロップの動作表 従って、下記のような回路構成にするとjkフリップフロップで、tフリ ップフロップを実現することができる。 q q ck k t j clock jkフリップフロップによるtフリップフロップ① q q ck k 論理1 j t

フリップフロッ プ 自己 保持 回路 これ フリップフロップは複数で使うのが一般的 プロセス文を記述するとき,一般に1個のフリップフロッ プだけを記述するために用いることはまれです.たいていの場 合,複数のフリップフロップからなる回路となりエダップテクノメド ソノリス アイムーブ ビジオトラック ECL Quanta System Quanta Litho レーザ Quanta Litho EVO レーザ Cyber Ho 60W Cyber Ho 100W Cyber TM Quanta Cyber Blade LABORIE AQUARIUS® CTS AQUARIUS® LT GOBY™ TDOC® フローマスター フロースター injeTAK® ROCAMED BIFLEX EVO KOBOTT型フリップフロ ップ510,5,530のロック解除確認後、1ビ ットカウンタ4へ有効エッジが印加される。その有効エ ッジの印加タイミングを調整するのが、タイミング制御 回路14である。

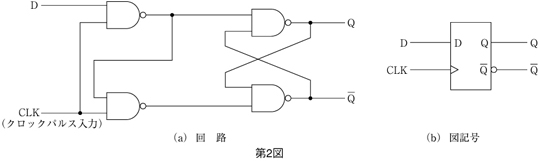

このフリップフロ ップ回路は、原則的に前記図6に示したラッチ回路の2 個を直列に接続したものである。 前段のマスター回路は 図6のラッチ回路と全く同様の構成であり、インバータ iv01、iv02、iv03、トランスミッションゲ ートtg01、tg02から構成される。D フリップフロップ内部をもうすこし詳しく見てみる.フリップフロップはラッチと フリップフロップを理解する トランジスタ技術 呼ばれます.SRフリップフロップと呼ばれることも ありますが,本稿ではSRラッチとしてフリップフロ ップと区別します.以降のSRラッチに制御端子を付 け足したものをフリップフロップとします. S T フリップフロッ プ>tff 回路図T型フリップフロ ップ510,5,530のロック解除確認後、1ビ ットカウンタ4へ有効エッジが印加される。その有効エ ッジの印加タイミングを調整するのが、タイミング制御 回路14である。 センサ回路

フリップフロップ

マイクラ ボタンでon Off切り替える小型のtフリップフロップ回路を色々探してみた 役に立つと思っている

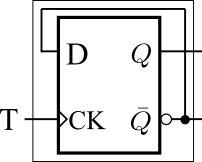

最初に、RSTフリップフロップを使った実現方法を示す。 次の回路では、入力信号Dの値を変更しても、それが出力に伝わるのは、入力信号Tの値が1のときである。 現時刻の入力信号 D, T および出力信号 Q, Q の値をそれぞれ i0, t0 および o0, o1 で表す。のリン脂質のフリップフロップに対する膜貫通配列 中の親水性残基の効果を評価した.フリップフロッ プの測定にはc6nbdpc という蛍光脂質を用いた. この実験系では,c6nbdpc分子はまず,luvの外 葉のみに組み込まれ,ペプチドのフリップフロップソフトエラーは,α線や中性子線等の粒子線がフリップフロッ プやSRAM に衝突することで記憶値を直接反転させるSEU (Single Event Upset) と,組み合わせ回路の近傍に衝突し一過 性のパルスが生じるSET (Single Event Transient) がある。組

フリップフロップ

論理回路 Logic Circuit Kanetaiの二次記憶装置

1回押すとON もう一度押すとOFFという回路を ラッチリレーを使っ 電子工作 回路編10トランジスタ2石のRSフリップ ;フリップフロップとカウンタ 公益社団法人 日本電気技術者協会 ある入力信号によって信号が出力され、入力信号が取り去られると元の状態に戻る。 フリップフロップ(FF:flipflop)回路は二進法の基本である情報を一時的に"0"または"1"の状態として保持1 テーマ フリップフロップとその応用 クラス 電気電子工学科4年 実験番号 491 担当 望月孔 New ;

マインクラフトpe対応 極小tフリップフロップ マイクラ Youtube

アップダウンカウンタの制作 基礎編 マルツセレクト

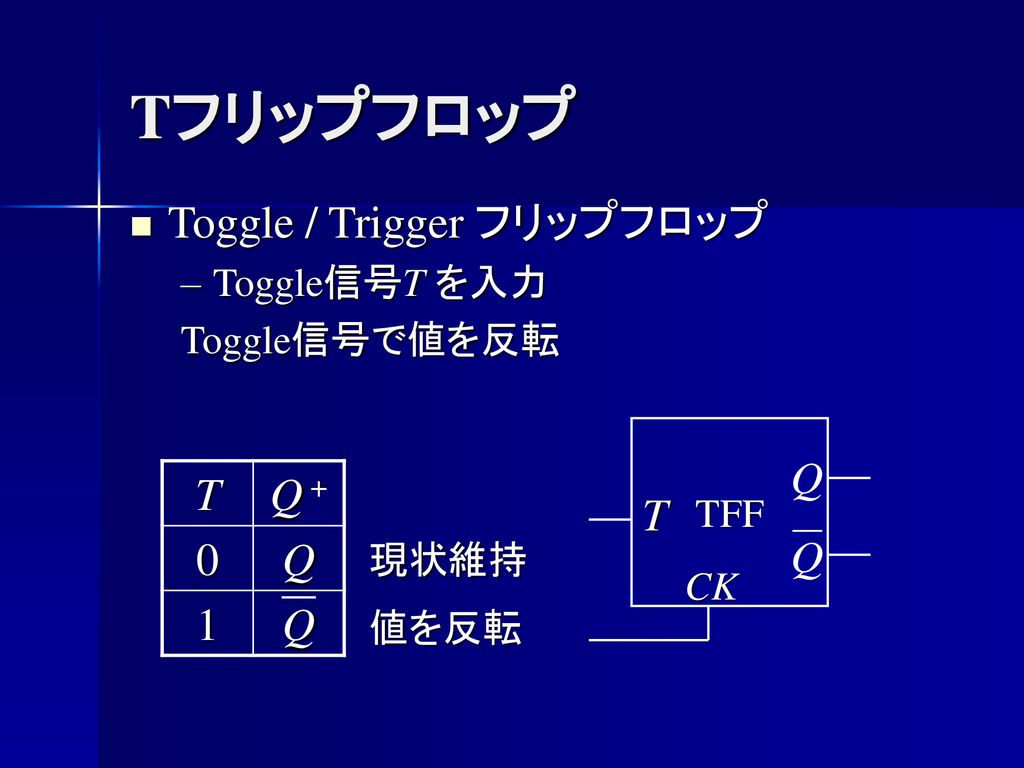

フリップフロップ ¶ フリップフロップは 1bit のデータを記憶する回路である。 入力信号により1または0を記憶し、値の変更を指示する信号が 入力されるまでは、最後に記憶した値を保持し出力し続ける。22 tff (トグル フリップフロップ) この tff は、 トグル 、もしくは トリガーフリップフロップ の略で、入力 t の立ち上りで、出力 q が反転します この tff の 遷移表 は、以下のようになります。 この表の左半分から論理式を求めます。フリップ・フロップ リレー回路 TSYSTEM;

フリップフロップ

Exploreroots D To T Flipflop Conversion

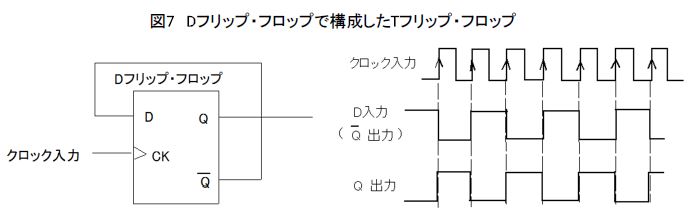

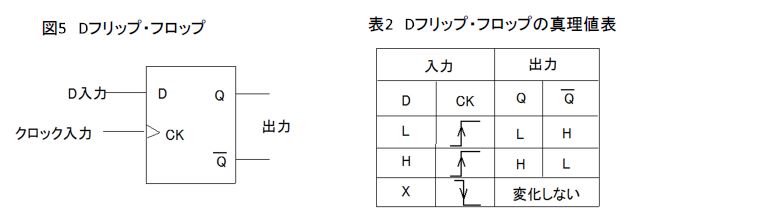

プl 9 が点灯してい 尚,d フリップフロップは次のt フリップフロップの構成に用いるので,d 前節のクロック端子付きrs フリップフロップを一部変更し,セット優先rs フリップフロ ップDフリップフロップ(D-FF) TC74HC273AP TC74HC273AP 通販コード I 発売日 メーカーカテゴリ 株式会社東芝セミコンダクター社 (TOSHIBA) 東芝のCMOSロジックIC、Dタイプフリップフロップ (DFF)です。 CMOSの低消費電力とLSTTLに匹敵する高速動作を兼ね備えています。 こちらはお客様からご要望を頂き販売開始いたました。 各種部品、半導体、機端子Dは常に端子C 図4-4(a)の回路はSRラッチ(Set-Reset latch)と 呼ばれます.SRフリップフロップと呼ばれることも ありますが,本稿ではSRラッチとしてフリップフロ ップと区別します.以降のSRラッチに制御端子を付 け足したものをフリップフロップとし

Wgexの使い方 フリップフロップ Pukiwiki

マイクラ Tフリップフロップの解説と作り方 隠しドアなどにも Youtube

フリップフロッ プ 回路 図 T フリップフロッ プ>tff 回路図 ~ 最高の壁紙HD論理回路:RSフリップフロップ回路 RSフリップフロップ回路 RSフリップフロップ回路のRはリセット、Sはセットの略です。 フリップフロップに記憶機能を持たせるためには、出力状態を入力にフィードバックすることで出力状態を保持する必要があります · うさぎでもわかる計算機システム Part08 フリップフロップ(D・T・RS・JK)・クロックとタイミングチャートの書き方 19年7月日 19年7月日 11分22秒 momousa787 こんにちは、ももやまです。 今回は順序回路であるフリップフロップについての説明をしたいと

Tフリップフロップの意味 用法を知る Astamuse

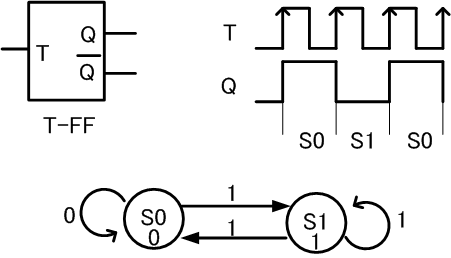

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

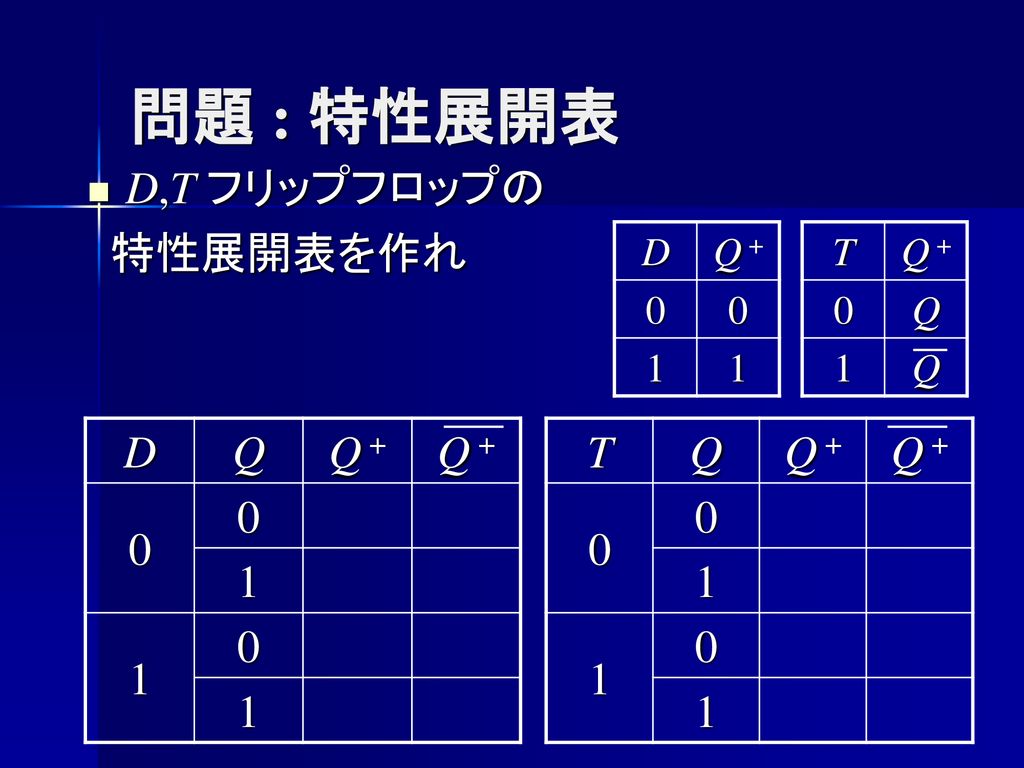

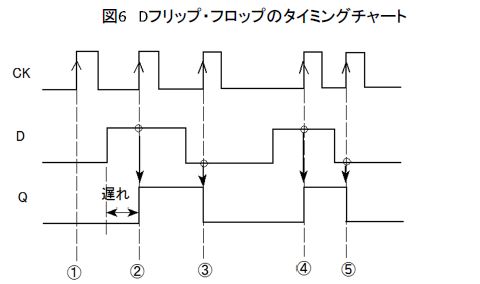

3 図3:フリップフロップのタイミングチャート 4 タイプのフリップフロップを挙げたが,設計の容易さから一般的にd フリップフロッ jk フリップフロッ プ 特性 表 jkフリップフロップの動作特性 q=0の状態で,j=0を入力すると,q=0を保持する q=0の状態で,j=1を入力すると,q=1に遷移する q23 フリップフロップ(FF) 順序回路を構成する重要な部品である記憶素子(メモリ)は、通常多数のラ ッチ(latch)やフリップフロップと呼ばれるものによって構成されている。ラ ッチやFFは1ビットの記憶素子であり、いくつかの種類がある。下図の基本論理ゲートで構成した回路(1)と シミュレータ内に登録されているjkフリップフロップ(2)が どちらも クロック信号(ck)に同期して教科書p66, 図107 に示してある動作をし, jkフリップフロップとして機能することを確認せよ.

ディジタル技術検定試験3級の問題と解説 Flip Flop An Engineer19のブログ

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

2回路Dフリップフロップ TC74HC74AP tc74hc74ap 通販コード i 発売日 メーカーカテゴリ 株式会社東芝セミコンダクター社(toshiba) 汎用のロジックicです、2回路入りdフリッププロップ tc74hc74a pdfデータシート2 JKフリップフロップ 入出力特性 Q(t1) = J(t) Q(t) ⋁ ~K(t) Q(t) S=J, R=Kの___FFとみなすことも出来る J=K=1の時は,入力を反転 J K Q Q 0 0 1 1 1 0 0 1 K J Q(t) Q(t1)のカルノー図 入力 出力フリップフロッ プ オルタネート(フリップフロップ)回路オムロンではdifu(立ち上がり微分)、三菱では pls(パルス)という命令を使いま この記事では、ラダープログラムにおけるフリッカー回路の練習問題を3ヶ出題します。

Jkフリップフロップ Dフリップフロップ Tフリップフロップ Yahoo 知恵袋

Tフリップフロップの真理値表や回路図を分かりやすく簡単に解説 なんとなくわかる 大学の数学 物理 情報

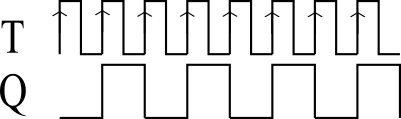

Tフリップフロップの動作表 jkフリップフロップの動作表 (oe ) によりコントロールされる独立な8 ビットのフリップフロッ プで構成されます。 また、"H" レベルのOE 信号により出力を高イ ンピーダンス状態にできるため、バスラインへのインタフェースが 容易です。T型フリップフロ ップ510,5,530のロック解除確認後、1ビ ットカウンタ4へ有効エッジが印加される。その有効エ ッジの印加タイミングを調整するのが、タイミング制御 回路14である。 Title 小胞体膜のリン脂質フリップフロップ制御機構に関するT Clock CK Clock T Q t1 t2 t3 t4 ε ε クロック入力付きフリップフロップ 状態変化はクロックに同期 クロックが立ち下がった時から遷移が始まる回路が多い T入力は任意の幅を持って良い 但しクロックが立ち上がって、下がるまで間とそのわずかな前後 は変化禁止。

Computer Archtecture

アップダウンカウンタの制作 基礎編 マルツセレクト

D(Delay),T(Toggle),JK などの種類がある.電源投入時には,ラッチ/フリップフロッ プは,ランダムに「1」または「0」の状態になるので,パワーオンリセットを用いて,電源 投入時に出力値が任意に「1」または「0」になるように JKフリップフロップ J K Q 0 1 0 みんなで作る知恵袋 悩みや疑問、なんでも気軽にきいちゃおう!

フリップフロップ

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

T Flip Flop To D Flip Flop Conversion Youtube

フリップフロップ Wikipedia

フリップフロップ

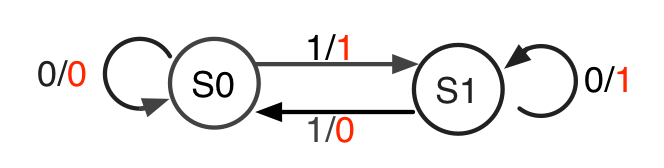

ミーリ マシンの状態遷移図例 石丸技術士事務所 ディジタル技術資料

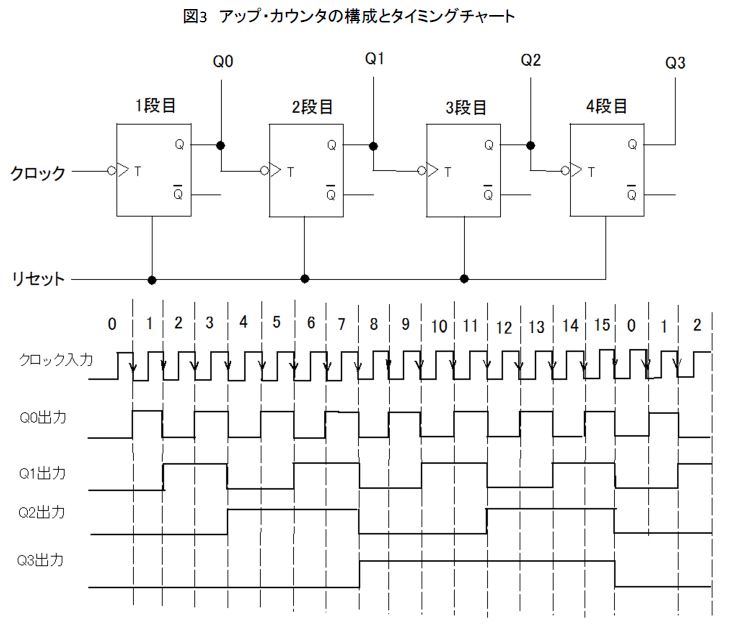

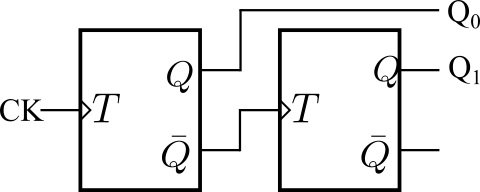

カウンタとシフトレジスタ Cpuを作ろう 計算機教材とマイコンと電子工作 楽天ブログ

記憶素子 フリップフロップ

状態遷移図 石丸技術士事務所 ディジタル技術資料

Computer Archtecture

マイクラ ボタンでon Off切り替える小型のtフリップフロップ回路を色々探してみた 役に立つと思っている

フリップフロップについて質問です Jk Ffでt Ffを作った Yahoo 知恵袋

ディジタル技術検定試験3級の問題と解説 Flip Flop 続き An Engineer19のブログ

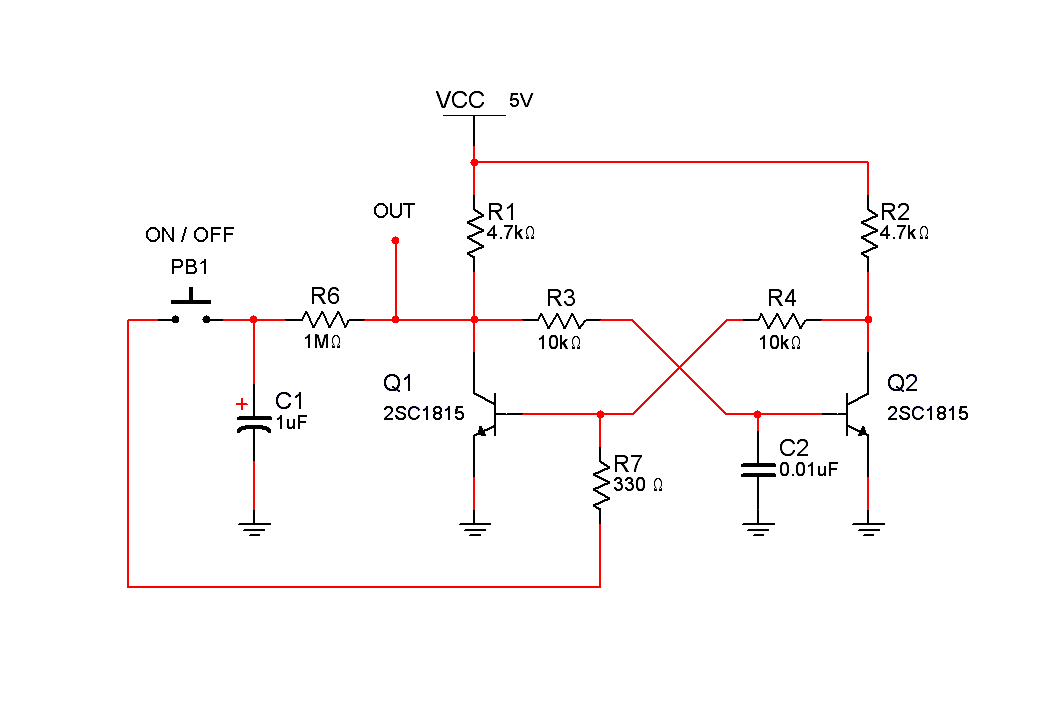

楊子平 در توییتر メモ シンプルな1ボタンでon Offのトグルが出来る回路 Tフリップフロップ 随分昔の回路だが ディスクリートトランジスタとして これより簡単な構成はないと思う 普通はダイオード2枚が必要

フリップフロップ

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 レーダー 基礎理論編

フリップフロップ

同期カウンタと非同期カウンタ 石丸技術士事務所 ディジタル技術資料

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk クロックとタイミングチャートの書き方 工業大学生ももやまのうさぎ塾

Introduction To T Flip Flop Youtube

Tはトグル用です Tフリップフロップの理解 ニュース 21

フリップフロップ

Basicプログラミング

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

Tフリップフロップ

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

過去問h28国家一般職 電気 電子 情報 No31 解説 公務員試験 これでok

アップダウンカウンタの制作 基礎編 マルツセレクト

論理回路 フリップフロップの動作原理 Youtube

デジタル回路設計入門

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

マスタスレーブtフリップフロップの問題を解いていたのですが だんだ 工学 教えて Goo

Computer Archtecture

Untitled Document

初心者注意 Tフリップフロップ解説 マイクラpe0 13で使える Youtube

電子回路に関する質問です 基本ロジック回路やtフリップフロッ Yahoo 知恵袋

Untitled Document

フリップフロップ

アップダウンカウンタの制作 基礎編 マルツセレクト

早わかり電子回路 順序回路とは フリップフロップの種類と同期の方法を学ぶ アイアール技術者教育研究所 製造業エンジニア 研究開発者のための研修 教育ソリューション

情報画像学実験ii 実験1 論理回路

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

Minecraft 3 3 1 の T Ff回路 無音 Ver1 4 2 ニコニコ動画

至急 論理回路の設計について T Ffをd Ffで設計せよ と Yahoo 知恵袋

Tはトグル用です Tフリップフロップの理解 ニュース 21

フリップフロップ

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

T Flip Flop 回路 マイクラポケット辞典

小山 幸伸 Yukinobu Koyama 研究ブログ Researchmap

Dフリップフロップ

01 号 分周回路 Astamuse

Tフリップフロップの意味 用法を知る Astamuse

Tff 通信用語の基礎知識

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Tフリップフロップの意味 用法を知る Astamuse

フリップフロップ Wikipedia

Minecraft Tフリップフロップ Youtube

Tフリップフロップをご紹介 のんびりマイクラpe

フリップフロップ

Tフリップフロップ 石丸技術士事務所 ディジタル技術資料

フリップフロップ

バイポーラトランジスタによる T Flip Flop Ltspice 落書き ふるた技工所 てっこうしょ 楽天ブログ

Computer Archtecture

まさはる S Weblog 15年11月 アーカイブ

トランジスタの見た夢 その2 トランジスタの見た夢

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 レーダー 基礎理論編

フリップフロップ Wikipedia

Tフリップフロップの意味 用法を知る Astamuse

フリップフロップ回路 Youtube

Tはトグル用です Tフリップフロップの理解 ニュース 21

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

フリップフロップ

Ppt コンピュータアーキテクチャ I 10 各種フリップフロップと 順序回路 Powerpoint Presentation Id

T型フリップフロップとカウンタ パソコンの選び方と買い方

フリップフロップ

Digital Circuit Lab4

0 件のコメント:

コメントを投稿